# NMOS UNIVERSAL PERIPHERAL INTERFACE 8-BIT MICROCOMPUTER

# **MBL8742H/N**

October 1986 Edition 1.0

#### DESCRIPTION

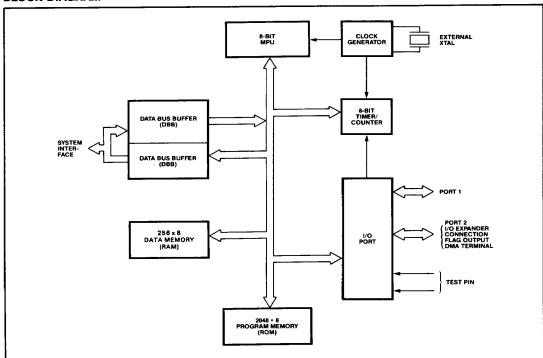

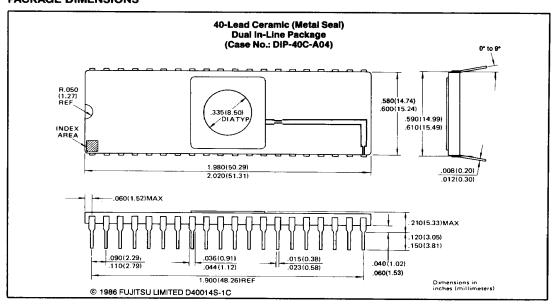

The Fujitsu MBL8742 Universal Peripheral Interface (UPI) is an 8-bit microcomputer that uses a 2K × 8-bit Electrically Programmable Read Only Memory (EPROM). Besides the EPROM program memory, the microprocessing circuits are supported by a 256 × 8-bit static RAM, 18 I/O lines, an 8-bit timer counter, and a clock generator. The device can be ordered in either of two speed versions: N-version for operation at 6MHz and H-version for operation at 12MHz. For either frequency, the operating temperature is 0°C to 70°C.

The MBL8742 is fabricated using an N-channel polysilicon-gate MOS process and is housed in a 40-pin ceramic windowed DIP. A single +5-volt supply is required for basic operation; the EPROM requires an ultraviolet (UV) light source for erasure and a 21-volt supply for programming.

Using the EPROM program memory, the MBL8742 is ideally suited for such applications as system evaluation, system prototyping, and low-volume production work.

#### **FEATURES**

- Processor: 8-bit Microprocessing Unit (MPU)

- Memories: 2K × 8-bit Program Memory (EPROM) 256 × 8-bit Data Memory (static RAM)

- 8-level Stack

- 8 pairs of Working Registers

- I/O: One 8-bit Bidirectional Data Bus Two 8-bit Bidirectional I/O Ports Two Test Inputs

- Master Processor Interface: One 8-bit Status Register

Two 8-bit Data Bus Buffer

- Registers

- DMA Handshake Capability

- 8-bit Timer/Event Counter

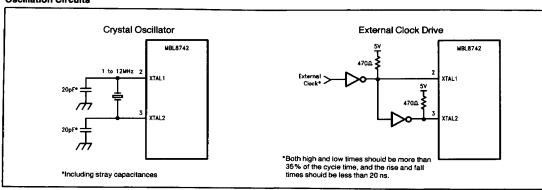

- Clock Source: Internal Clock Generator (with external Crystal) or External Clock

- Single-step Operation

- Low-power RAM Retention Mode

- Power-on Reset Capability (with External Capacitor)

- Instruction Cycle: 1.25μs/12MHz (MBL8742H) and 2.5μs/6MHz (MBL8742N)

- Instruction Set: 93 Instructions with 217 Instruction Codes

- Single +5V Power Supply

- Operating Temperature Range: 0°C to 70°C

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However it is advised that normal precautions be taken to avoid application of any voltage higher than maximum voltages to this high impedance circuit.

Portions reprinted by permission of Intel Corporation, Copyright © 1986 Intel Corporation, Compilation and additional materials Copyright © 1986 by Fujitsu Limited, Tokyo, Japan, and Fujitsu Microelectronics, Inc., Santa Clara, California, U.S.A. Fujitsu Limited is a licensee of Intel Corporation and authorized to produce alternate source products.

#### **FEATURES (Cont)**

- N-channel Silicon-gate MOS Process

- Standard 40-pin Ceramic DIP (Suffix-C)

- Compatible with Intel 8742

- Replaceable with MBL8041A/42 and Intel 8041A/42

#### **BLOCK DIAGRAM**

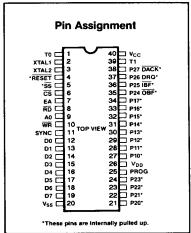

#### PIN DESCRIPTIONS

| Pin No. | Symbol          | Function                                                                                                                          |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 40      | V <sub>CC</sub> | +5Vdc power supply input.                                                                                                         |

| 26      | V <sub>DD</sub> | +5Vdc power supply input for internal RAM.  This pin is also used as the power supply input when programming the EPROM.           |

| 20      | V <sub>SS</sub> | Ground terminal.                                                                                                                  |

| 1       | ТО              | Input used for conditional branching.                                                                                             |

| 39      | T1              | This pin performs the following functions:  Event input pin for the event counter.  Conditional input pin for conditional branch. |

# PIN DESCRIPTIONS (Cont)

| Pin No. | Symbol  | Function                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | XTAL 1  | Input connection for external crystal.                                                                                                                                                                                                                                                                                                                        |

|         |         | This pin can also be used as an input from an external clock source.                                                                                                                                                                                                                                                                                          |

| 3       | XTAL 2  | Input connection for external crystal.                                                                                                                                                                                                                                                                                                                        |

|         |         | (Note: The XTAL 1 and XTAL 2 input levels are not directly TTL compatible with a TTL clock source. An open-collector drive with an appropriate pullup is required to properly interface the two circuits.)                                                                                                                                                    |

| 4       | RESET   | Input that resets and initializes the MPU.                                                                                                                                                                                                                                                                                                                    |

|         |         | (Note: This input level is not TTL compatible.)                                                                                                                                                                                                                                                                                                               |

| 5       | SS      | Input used for single step operation.                                                                                                                                                                                                                                                                                                                         |

| 6       | CS      | Chip select input.                                                                                                                                                                                                                                                                                                                                            |

| 7       | EA      | Input used for controlling program memory access. Holding EA high forces all program memory fetches to reference external memory. Useful for emulation and debug, and essential for testing and program verification.                                                                                                                                         |

| 8       | RD      | Strobe that enables a read operation from data bus buffer or status register.                                                                                                                                                                                                                                                                                 |

| 9       | A0      | Address input to determine whether read/write data or read/write commands.                                                                                                                                                                                                                                                                                    |

|         |         | A0 = "L" indicates data read or write. A0 = "H" indicates status read or command write.                                                                                                                                                                                                                                                                       |

| 10      | WR      | Strobe that enables a write operation to data bus buffer register.                                                                                                                                                                                                                                                                                            |

| 11      | SYNC    | An output synchronized with the MBL8742 clock. This pin is used when a synchronization signal is required for external circuits.                                                                                                                                                                                                                              |

| 12-19   | D0-D7   | 8-bit bidirectional I/O port used to interface the MBL8742 to the master processor.                                                                                                                                                                                                                                                                           |

| 21-24   | P20-P23 | Lower 4 bits of the 8-bit quasi-bidirectional I/O port (Port 2). These pins function as an interface port with the I/O expander (MBL8243) when an expansion I/O is used to execute instructions. During single step operation the upper 3 bits of the program address are output on P20, P21, P22.                                                            |

| 35-38   | P24-P27 | Upper 4 bits of the 8-bit quasi-bidirectional I/O port (Port 2). These function as the flag output pins (P24 and P25) and DMA pins (P26 and P27) according to the executed instruction.  P24: OBF (Output Data Buffer Register Full) output P25: IBF (Input Data Buffer Register Full) output P26: DRQ (DMA Request) output P27: DACK (DMA Acknowledge) input |

| 25      | PROG    | Strobe output signal when performing an expansion I/O instruction with an I/O expander such as the MBL8243.                                                                                                                                                                                                                                                   |

|         |         | Used as a programming input when writing to the EPROM.                                                                                                                                                                                                                                                                                                        |

| 27-34   | P10-P17 | 8-bit Quasi-bidirectional I/O ports (Port 1). During single step operation, the next program fetch address (Lower 8 bits) is output from these pins.                                                                                                                                                                                                          |

#### **FUNCTIONAL DESCRIPTION**

#### **System Interface**

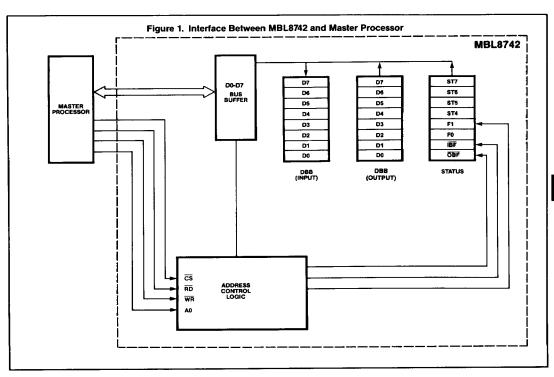

The data, command, and status interface between the master processor and the MBL8742 is provided by two Data Bus Buffer(DBB) registers and a status register. Selection logic for these registers is shown in Table 1; a simplified interface is shown in Figure 1. Referring to the interface drawing, note that the master processor can read data from the output buffer register and write data into the input buffer register. When the MBL8742 executes an "OUT DBB, A" instruction, data is written into the DBB and the Output Buffer Full (OBF) flag is set. When data is read from the DBB by the master processor, OBF is reset. If the master processor writes into DBB, the Input Buffer Full (IBF) flag is set and is reset when the MBDL8742 reads the data. Reading the status register is non-destructive and does not affect internal operation of the MBDL8742.

Table 1. Selection Logic

| CS | RD | WR | AO | DESCRIPTION                           |

|----|----|----|----|---------------------------------------|

| 0  | 0  | 1  | 0  | Read DBB (Output) register.           |

| 0  | 0  | 1  | 1  | Read STS (Output) register (Status)   |

| 0  | 1  | 0  | 0  | Write DBB (Input) register (Data).    |

| 0  | 1  | 0  | 1  | Write DBB (Input) register (Command). |

| 1  | х  | ×  | ×  | Invalid.                              |

#### **Program Status Word (PSW)**

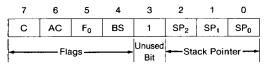

As shown in the following diagram and associated text, the upper four bits of the PSW are used as flags to indicate MPU status. The lower three bits are used to select register pairs in the RAM stack when servicing a subroutine call or an interrupt. The flag bits (C, AC,  $F_0$ , and BS) are defined below; the stack pointer bits (SP $_0$ -SP $_2$ ) are defined in the next paragraph. The remaining bit in the PSW is unused.

#### Flag Bits

**C (Carry):** When an accumulator overflow occurs during an ALU operation, this bit is set to '1'.

**AC (Auxiliary Carry):** When an accumulator overflow from bit 3 to bit 4 occurs during an addition, this bit is set to "1".

$F_0$  (User Flag): With the proper instruction, this flag can be user-designated; the  $F_0$  flag can also be checked from the MPU as bit 2 of the Status Register.

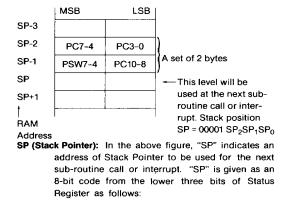

**BS (Bank Select):** With the proper instruction, the BS flag indicates selection of a Register Bank. When set to "0", Register Bank 0 is selected; when set to "1", Register Bank 1 is selected. Refer to the RAM memory map that follows.

#### Stack Register (8-Level Capability)

The Stack Register has 16 bytes of memory area in the built-in RAM. The stack Register consists of eight levels, that is, a stack level consists of two bytes as shown in the following diagram.

SP = 00001SP<sub>2</sub>SP<sub>1</sub>SP<sub>0</sub>

Status Register Bits 0 to 2.

PC<sub>n</sub> (Program Counter): In the above figure, "PC<sub>n</sub>" indicates the content of the n-th bit in the Program Counter.

#### **RESIDENT DATA MEMORY MAP (RAM)**

#### MBL8742H/N

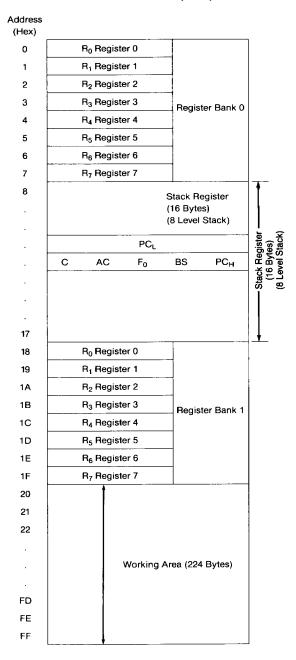

#### Interrupt Processing

There are two types of interrupt:  $\overline{IBF}$  interrupt and Timer/Counter interrupt. If an interrupt occurs when the system is in "interrupt enable" status, the interrupt flag is set as soon as the current instruction is completed and interrupt processing starts.

First, the upper four bits of the Status Word and content of the Program Counter are stored in the stack. The program then jumps to address "3" in the case of an  $\overline{\text{IBF}}$  interrupt and address "7" in the case of a Timer/Counter interrupt.

After the interrupt has been processed by a user program and a RETR (Return and Restore Status) instruction has been executed, the Status Word and Program Counter contents stored in the stack are restored, the interrupt flag is reset, and the system is ready to accept the next interrupt request.

A Timer/Counter interrupt request occurs when the Timer/Counter overflow flag is set due to Timer/Counter overflow. However, since the Timer/Counter interrupt request is masked by the  $\overline{IBF}$  interrupt request, an  $\overline{IBF}$  interrupt has first priority.

The Timer/Counter interrupt is enabled after the IBF interrupt has been executed and the system is now ready to receive the next interrupt request. Operational and interrupt flowcharts are shown on the following page.

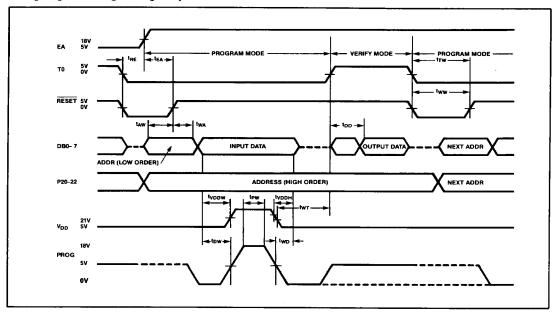

#### PROGRAMMING AND VERIFYING THE EPROM

The MBL8742 uses an internal 2K  $\times$  8 EPROM for program memory. A description of the pins used for programming and verifying operation of the EPROM are repeated here for user convenience. Procedural steps for programming and verification follow the pin functions.

#### Pin Descriptions

| Symbol        | Function                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------------|

| XTAL1 & XTAL2 | Input clock signal (1-to-3MHz)                                                                             |

| RESET         | Initializes internal registers.                                                                            |

|               | Input address data to the data bus is internally latched on the rising edge of $\overline{\text{HESET}}$ . |

| то            | When T0 is Low, program mode is selected.                                                                  |

|               | When T0 is High, verify mode is selected.                                                                  |

| EA            | When 18-volts is applied to this pin, the program and verify modes are enabled.                            |

| Bus (D7-D0)   | Lower 8-bits for address and data inputs in the program mode; data output in the verify mode.              |

| P22-P20       | Upper address inputs.                                                                                      |

| Symbol          | Function                        |

|-----------------|---------------------------------|

| V <sub>DD</sub> | +5-volt power supply.           |

| PROG            | Input programming pulses.       |

| A0 & CS         | Clamp both of these inputs low. |

#### **Programming Procedures**

Step 1: Initialize circuits as follows.

- Apply +5V to V<sub>CC</sub>, V<sub>DD</sub>, T0 and EA pins. Let Bus (D7-D0) and PROG pins float.

- Apply 0V to RESET, A0, and CS pins.

- Use internal oscillator or an external source to generate a 1-to-3MHz clock.

- Step 2: Select program mode by setting T0 to 0V.

- Step 3: Set EA to 18V to enable program or verify mode.

- Step 4: Input address as follows.

- Bus (D7-D0): 8 low-order bits

- P22 to P20: 3 high-order bits

- Step 5: Set RESET to +5V to internally latch address inputs.

- Step 6: Input write data to bus.

- Step 7: Turn on programming power supply and set V<sub>DD</sub> to 21-yolts.

- Step 8: Apply 0-volts to the PROG pin and then apply a programming pulse of 18-volts for 50-milliseconds. Again apply 0-volts to the pin and then let it float.

- Step 9: Turn off programming power supply ( $V_{DD}$  from 21V to 5V) and let Bus (D7-D0) float.

- Step 10: Select verify mode by setting T0 to 5V.

- Step 11: Read and verify bus data. If data cannot be verified, repeat steps 2 through 10.

- Step 12: Set RESET to 0V. If all desired addresses haven't been written yet, repeat steps 4 through 11.

- Step 13: Set EA to 5V to terminate programming procedure.

#### **ERASING THE EPROM**

Data written into the EPROM can be erased by applying ultraviolet light rays with a wavelength of 2537 angstroms. With UV light source directly above the transparent lid at a distance of 2-to-3 centimeters. The time for complete erasure is between 15-and-20 minutes for most commercial lamps. The recommended amount of UV radiation is 10Wsec/cm²; the luminous intensity on the package surface is designed to be approximately 12000uW/cm².

If the package surface is soiled by grease, adhesives, or other light inhibitors, the erasing time will increase. Before attempting to erase data, it is recommended that surfaces be cleaned with alcohol or some other detergent that will not damage the package.

#### **OPERATIONAL FLOWCHART**

#### INTERRUPT FLOWCHART

4-170

**Table 2. Instruction Set Summary**

| ACCUMULATOR INSTRUCTIONS        |               | <del></del> |      | T        |            |            |                                         |

|---------------------------------|---------------|-------------|------|----------|------------|------------|-----------------------------------------|

|                                 |               | OP          |      |          | Flag       |            |                                         |

| Operation                       | Mnemonic      | code        | Byte | Cycle    | С          | AC         | Remarks                                 |

| Add register to A               | ADD A, Rr     | 6X3         | 1    | 1        | <b>*</b> 2 | *2         | (A) ← (A) + (Rr)                        |

| Add data memory to A            | ADD A, @R0    | 60          | 1    | 1        | <b>*</b> 2 | <b>*</b> 2 | (A) ← (A) + ((R0))                      |

| •                               | ADD A, @R1    | 61          | 1    | 1        | <b>*</b> 2 | <b>*</b> 2 | (A) ← (A) + ((R1))                      |

| Add immediate to A              | ADD A, #data  | 03          | 2    | 2        | *1         | <b>*</b> 2 | (A) ← (A) + data                        |

| Add register to A with Carry    | ADDC A, Rr    | 7X3         | 1    | 1        | *1         | <b>*</b> 2 | $(A) \leftarrow (A) + (Rr) + (C)$       |

| Add data memory to A with Carry | ADDC A, @R0   | 70          | 1    | 1        | <b>*</b> 1 | <b>*</b> 2 | (A) ← (A) + ((R0)) + (C                 |

| •                               | ADDC A, @R1   | 71          | 1    | 1        | *1         | <b>*</b> 2 | (A) ← (A) + ((R1)) + (C                 |

| Add immediate to A with Carry   | ADDC A, #data | 13          | 2    | 2        | *1         | <b>*</b> 2 | (A) ← (A) + data + (C)                  |

| AND register to A               | ANL A, Rr     | 5X3         | 1    | 1        | -          | -          | (A) ← (A) AND (Rr)                      |

| AND data memory to A            | ANL A, @R0    | 50          | 1    | 1        | -          | -          | (A) ← (A) AND ((R0))                    |

| , ,                             | ANL A, @R1    | 51          | 1    | 1        | -          | -          | (A) ← (A) AND ((R1))                    |

| AND immediate to A              | ANL A, #data  | 53          | 2    | 2        | -          | -          | (A) ← (A) AND data                      |

| OR register to A                | ORL A, Rr     | 4X3         | 1    | 1        | -          | -          | (A) ← (A) OR (Rr)                       |

| OR data memory to A             | ORL A, @R0    | 40          | 1    | 1        | -          | -          | (A) ← (A) OR ((R0))                     |

| on data memory to A             | ORL A, @R1    | 41          | 1    | 1        | _          | -          | (A) ← (A) OR ((R1))                     |

| OR immediate to A               | ORL A, #data  | 43          | 2    | 2        | -          | _          | (A) ← (A) OR data                       |

| Exclusive OR register to A      | XRL A, Rr     | DX3         | 1    | 1        | _          | -          | (A) ← (A) XOR (Rr)                      |

| _                               | XRL A, @R0    | DO          | 1    | 1 1      | _          | _          | (A) - (A) XOR ((R0))                    |

| Exclusive OR data memory to A   | XRL A, @R1    | D1          | 1    | i        | _          | _          | (A) ← (A) XOR ((R1))                    |

| 5 1 1 0 0 0 increased in the A  | XRL A, @AT    | D3          | 2    | 2        | _          | _          | (A) ← (A) XOR data                      |

| Exclusive OR immediate to A     |               | 17          | 1    | 1        | _          | _          | (A) ← (A) + 1                           |

| Increment A                     | INC A         | 07          | 1    | 1 1      | _          | _          | (A) ← (A) – 1                           |

| Decrement A                     | DEC A         | 27          | 1    | '1       | _          |            | (A) ← 0                                 |

| Clear A                         | CLR A         |             |      |          | -          | _          | $(A) \leftarrow (\overline{A})$         |

| Complement A                    | CPL A         | 37          | 1    |          | *          |            | Note 2                                  |

| Decimal Adjust A                | DA A          | 57          | 1 1  | 1        | ^          | -          | (A7-4) <del>←</del> (A3-0)              |

| Swap digits of A                | SWAP A        | 47          | ] ]  | '        | -          | -          | (A7-4) 42 (A3-0)                        |

| Rotate A Left                   | RL A          | E7          | 1    | 1        | -          | -          | [ <del>7]=  1]</del>                    |

| Rotate A Left through Carry     | RLC A         | F7          | 1    | 1        | *1         | -          | C 7 0<br>□-Ⅲ                            |

| Rotate A Right                  | RR A          | 77          | 1    | 1        | -          | -          | 7 0<br>►\\\ <del> </del>                |

| Rotate A Right through Carry    | RRC A         | 67          | 1    | 1        | *1         | -          | C 7 0                                   |

| INPUT/OUTPUT INSTRUCTIONS       |               |             |      | <u> </u> |            | -          |                                         |

| Input port to A                 | IN A, P1      | 09          | 1    | 2        | T          | -          | (A) ← (P1)                              |

| Input port to A                 | IN A, P2      | OA          | 1    | 2        | _          | 1 -        | (A) ← (P2)                              |

| Output A to port                | OUTL P1, A    | 39          | 1    | 2        | _          | _          | (P1) ← (A)                              |

| Output A to port                | OUTL P2, A    | 3A          | 1    | 2        | _          | _          | (P2) ← (A)                              |

| AND immediate to part           | ANL P1, #data | 99          | 2    | 2        | _          | _          | (P1) ← (P1) AND data                    |

| AND immediate to port           | ANL P1, #data | 9A          | 2    | 2        | -          | -          | (P2) ← (P2) AND data                    |

| OB to a distant                 | · ·           | 89          | 2    | 2        | [          | -          | (P1) ← (P1) OR data                     |

| OR immediate to port            | ORL P1, #data | 89<br>8A    | 2    | 2        | -          | -          | (P2) ← (P2) OR data                     |

|                                 | ORL P2, #data |             | _    |          | -          | -          | (A) ← (DBB), (IBF) ←                    |

| Input DBB to A, clear IBF       | IN A, DBB     | 22          | 1    | 1        |            |            | 1 * * * * * * * * * * * * * * * * * * * |

| Output A to DBB, set OBF        | OUT DBB, A    | 02          | 1    | 1        | -          | -          | (DBB) ← (A), (OBF) ←                    |

| A7-4 to bits 7-4 of Status      | MOV STS, A    | 90          | 1    | 1        | 1 -        | i -        | (STS7-4) ← (A7-A4)                      |

|                                     |                | OP              |      |       | Flag     |          |                               |  |

|-------------------------------------|----------------|-----------------|------|-------|----------|----------|-------------------------------|--|

| Operation                           | Mnemonic       | code            | Byte | Cycle | С        | AC       | Remarks                       |  |

| Input Expander port to A            | MOVD A, Pp     | OX4             | 1    | 2     | -        | -        | (A3-0) ← (Pp),<br>(A7-4) ← 0  |  |

| Output A to Expander port           | MOVD Pp, A     | 3X4             | 1    | 2     | _        |          | (Pp) ← (A3–0)                 |  |

| AND A to Expander port              | ANLD Pp, A     | 9X4             | 1    | 2     | _        | _        | (Pp) ← (Pp) AND (A3-          |  |

| OR A to Expander port               | ORLD Pp. A     | 8X4             | 1    | 2     | -        | -        | (Pp) ← (Pp) OR (A3-0)         |  |

| DATA MOVE INSTRUCTIONS              |                | L               |      | L     | <u> </u> | <u> </u> |                               |  |

| Move register to A                  | MOV A, Rr      | FX3             | 1    | 1     | Π.       | Τ.       | (A) ← (Rr)                    |  |

| Move data memory to A               | MOV A, @R0     | F0              | 1    | 1     | _        | _        | (A) ← ((R0))                  |  |

|                                     | MOV A, @R1     | F1              | 1    | 1     |          |          | (A) ← ((R1))                  |  |

| Move immediate to A                 | MOV A, #data   | 23              | 2    | 2     | _        | ۱ ـ      | (A) ← data                    |  |

| Move A to register                  | MOV Rr. A      | AX3             | 1    | 1     | _        | _        | (Rr) ← (A)                    |  |

| Move A to data memory               | MOV @R0, A     | Α0              | 1    | 1     | -        | _        | ((R0)) ← (A)                  |  |

| ,                                   | MOV @R1, A     | A1              | 1    | 1     | _        | _        | ((R1)) ← (A)                  |  |

| Move immediate to register          | MOV Rr. #data  | BX3             | 2    | 2     | _        | _        | (Rr) ← data                   |  |

| Move immediate to data memory       | MOV @R0, #data | В0              | 2    | 2     | _        | _        | ((R0)) ← data                 |  |

|                                     | MOV @R1, #data | B1              | 2    | 2     | -        | _        | ((R1)) ← data                 |  |

| Move PSW to A                       | MOV A, PSW     | C7              | 1    | 1     | -        | _        | (A) ← (PSW)                   |  |

| Move A to PSW                       | MOV PSW. A     | D7              | 1    | 1     | *1       | *1       | (PSW) ← (A)                   |  |

| Exchange A and register             | XCH A, Rr      | 2X3             | 1    | 1     | -        | -        | (A) ≠ (Rr)                    |  |

| Exchange A and data memory          | XCH A, @R0     | 20              | 1    | 1     | _        | _        | (A) ≠ ((R0))                  |  |

| ,                                   | XCH A, @R1     | 21              | 1    | 1     | -        | -        | (A) ≠ ((R1))                  |  |

| Exchange digit of A and data memory | XCHD A, @R0    | 30              | 1    | 1     | -        | -        | (A3-0) ≠ ((R0)3-0)            |  |

|                                     | XCHD A, @R1    | 31              | 1    | 1     | -        | _        | (A3-0) <del>←</del> ((R1)3-0) |  |

| Move to A from current page         | MOVP A, @A     | А3              | 1    | 2     | -        | -        | (A) ← ((A)) within pag        |  |

| Move to A from Page 3               | MOVP3A, @A     | E3              | 1    | 2     | -        | -        | (A) ← ((A)) within page       |  |

| TIMER/COUNTER INSTRUCTIONS          | <u> </u>       |                 |      |       |          | <u> </u> | <u></u>                       |  |

| Read Timer/Counter                  | MOV A, T       | 42              | 1    | 1     | _        | _        | (A) ← (T)                     |  |

| Load Timer/Counter                  | MOV T. A       | 62              | 1    | 1     | _        | _        | (T) ← (A)                     |  |

| Start Timer                         | STRT T         | 55              | 1    | 1     | _        | _        | (-, (-,                       |  |

| Start Counter                       | STRT CNT       | 45              | 1    | 1     |          | _        |                               |  |

| Stop Timer/Counter                  | STOP TONT      | 65              | 1    | 1     | _        | _        |                               |  |

| Enable Timer/Counter Interrupt      | EN TCNTI       | 25              | 1    | 1     | _        | _        |                               |  |

| Disable Timer/Counter Interrupt     | DIS TONTI      | 35              | 1    | 1     | -        | -        |                               |  |

| CONTROL INSTRUCTIONS                |                |                 |      |       |          | <u>,</u> |                               |  |

| Enable DMA Handshake Lines          | EN DMA         | E5              | 1    | 1     | -        | -        |                               |  |

| Enable IBF Interrupt                | ENI            | 05              | 1    | 1     | -        | -        |                               |  |

| Disable IBF Interrupt               | DISI           | 15              | 1    | 1     | _        |          |                               |  |

| Enable Master Interrupts            | EN FLAGS       | F5              | 1    | 1     | -        | - 1      |                               |  |

| Select register bank 0              | SEL RB0        | C5              | 1    | 1     | -        | - :      | (BS) ← 0                      |  |

| Select register bank 1              | SEL RB1        | D5              | 1    | 1     | -        | -        | (BS) ← 1                      |  |

| No Operation                        | NOP            | 00              | 1    | 1     | -        | -        | , ,                           |  |

| REGISTER INSTRUCTIONS               |                |                 |      |       |          |          |                               |  |

| ncrement register                   | INC Rr         | 1X <sup>3</sup> | 1    | 1     | -        | -        | (Rr) ← (Rr) + 1               |  |

| Increment data memory               | INC @R0        | 10              | 1    | 1     | -        | -        | ((R0)) ← ((R0)) + 1           |  |

| •                                   | INC @R1        | 11              | 1    | 1     | -        | -        | ((R1)) ← ((R1)) + 1           |  |

| Decrement register                  | DEC Rr         | CX3             | 1    | 1     | l _      | l _      | (Rr) ← (Rr) - 1               |  |

# **MBL8742H/N**

|                                    |               | OP          |      |       | Flag |    |                                 |

|------------------------------------|---------------|-------------|------|-------|------|----|---------------------------------|

| Operation                          | Mnemonic      | code        | Byte | Cycle | С    | AC | Remarks                         |

| Jump to Subroutine                 | CALL addr     | <b>%4</b> 5 | 2    | 2     | -    | -  | Note 6                          |

| Return                             | RET           | 83          | 1    | 2     | -    | -  | Note 7                          |

| Return and restore status          | RETR          | 93          | 1    | 2     | *1   | *1 | Note 8                          |

| FLAGS INSTRUCTIONS                 |               |             |      |       |      |    |                                 |

| Clear Carry                        | CLR C         | 97          | 1    | 1     | Z¹   | -  | (C) ← 0                         |

| Complement Carry                   | CPL C         | A7          | 1    | 1     | CP1  | -  | (C) ← (C)                       |

| Clear Flag 0                       | CLR F0        | 85          | 1    | 1     | -    | -  | (F0) ← 0                        |

| Complement Flag 0                  | CPL F0        | 95          | 1    | 1     | -    | -  | (F0) ← ( <del>F0</del> )        |

| Clear Flag 1                       | CLR F1        | A5          | 1    | 1     | -    | -  | (F1) ← 0                        |

| Complement Flag 1                  | CPL F1        | B5          | 1    | 1     | -    | -  | (F1) ← (F1)                     |

| BRANCH INSTRUCTIONS                | •             |             |      |       |      |    |                                 |

| Jump unconditional                 | JMP addr      | <b>%4</b> 5 | 2    | 2     | -    | -  | Unconditional Branc             |

| Jump indirect                      | JMPP @A       | В3          | 1    | 2     | -    | -  | Unconditional Branc<br>(Note 9) |

| Decrement register and jump        | DJNZ Rr, addr | EX3         | 2    | 2     | -    | -  | (Rr) ≠ 0 (Note 10)              |

| Jump on Carry = 1                  | JC addr       | F6          | 2    | 2     | -    | -  | (C) = 1                         |

| Jump on Carry = 0                  | JNC addr      | E6          | 2    | 2     | -    | -  | (C) = 0                         |

| Jump on A Zero                     | JZ addr       | C6          | 2    | 2     | -    | -  | (A) = 0                         |

| Jump on A not Zero                 | JNZ addr      | 96          | 2    | 2     | -    | -  | (A) ≠ 0                         |

| Jump on T0 = 1                     | JT0 addr      | 36          | 2    | 2     | _    | -  | (T0) = H                        |

| Jump on T0 = 0                     | JNT0 addr     | 26          | 2    | 2     | -    | -  | (T0) = L                        |

| Jump on T1 = 1                     | JT1 addr      | 56          | 2    | 2     | -    | -  | (T1) = H                        |

| Jump on T1 = 0                     | JNT1 addr     | 46          | 2    | 2     | -    | _  | (T1) = L                        |

| Jump on F0 = 1                     | JF0 addr      | В6          | 2    | 2     | -    | -  | (F0) = 1                        |

| Jump on F1 = 1                     | JF1 addr      | 76          | 2    | 2     |      |    | (F1) = 1                        |

| Jump on Timer Flag = 1, Clear Flag | JTF addr      | 16          | 2    | 2     | -    | -  | (TF) = 1                        |

| Jump on IBF Flag = 0               | JNIBF addr    | D6          | 2    | 2     | -    | -  | (IBF) = 0                       |

| Jump on OBF Flag = 1               | JOBF addr     | 86          | 2    | 2     | -    | -  | (OBF) = 1                       |

| Jump on Accumulator Bit            | JBb addr      | <b>%2</b> 5 | 2    | 2     | -    | -  | (Ab) = 1                        |

#### Notes:

- 1. Flag status

- \* = Set or reset flag bit to the state it was in before instruction execution.

- Z = Reset flag bit.

- CP = Complement flag bit.

- The accumulator value is adjusted to form BCD digits following the binary addition of BCD numbers.

- 3. Refer to Table 3.

- 4. Refer to Table 4.

- Refer to Table 5.

- CALL addr

- ((SP)) ← (PC), (PSW7-4) (SP) ← (SP) + 1 (PC10-8) ← A<sub>H</sub> (PC7-0) ← A<sub>L</sub>

- 7. RET

- (SP) ← (SP) 1 (PC) ← ((SP))

- 8. RETR

- (SP) ← (SP) 1 (PC) ← ((SP))

- (PSW7-4) ← ((SP))

- 9. JMPP @A (PC7-0) ← ((A))

- (PC7-0) ← ((A)) 10. DJNZ Rr, addr (Rr) ← (Rr) 1 if (Rr) ≠ 0 (PC7-0) ← addr

- if (Rr) = 0 Execute next instruction

Table 3. OP Code for Register Access

| Rr            | RO | R1 | R2 | R3 | R4 | R5 | R6 | R7 |

|---------------|----|----|----|----|----|----|----|----|

| Mnemonic      |    |    |    |    |    |    |    |    |

| ADD A, Rr     | 68 | 69 | 6A | 6B | 6C | 6D | 6E | 6F |

| ADDC A, Rr    | 78 | 79 | 7A | 7B | 7C | 7D | 7E | 7F |

| ANL A, Rr     | 58 | 59 | 5A | 5B | 5C | 5D | 5E | 5F |

| DEC Rr        | C8 | C9 | CA | СВ | CC | CD | CE | CF |

| DJNZ Rr, addr | E8 | E9 | EA | EB | EC | ED | EE | EF |

| INC Rr        | 18 | 19 | 1A | 1B | 1C | 1D | 1E | 1F |

| MOV A, Rr     | F8 | F9 | FA | FB | FC | FD | FE | FF |

| MOV Rr, A     | A8 | A9 | AA | AB | AC | AD | ΑE | AF |

| MOV Rr, #data | B8 | B9 | ВА | вв | вс | BD | BE | BF |

| ORL A, Rr     | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |

| XCH A, Rr     | 28 | 29 | 2A | 2B | 2C | 2D | 2E | 2F |

| XRL A, Rr     | D8 | D9 | DA | DB | DC | DD | DE | DF |

|               |    |    |    |    |    |    |    |    |

Bit 7 6 5 4 3 2 1 0

Table 4. OP Codes for Expander Port Access

| Rr | P4  | P5             | P6                      | P7                   |

|----|-----|----------------|-------------------------|----------------------|

|    |     |                |                         |                      |

|    | 9C  | 9D             | 9E                      | 9F                   |

|    | OC. | 0D             | 0E                      | 0F                   |

|    | 3C  | 3D             | 3E                      | 3F                   |

|    | 8C  | 8D             | 8E                      | 8F                   |

|    | Rr  | 9C<br>0C<br>3C | 9C 9D<br>0C 0D<br>3C 3D | 0C 0D 0E<br>3C 3D 3E |

Bit 7 6 5 4 3 2 1 0

Table 5. OP Codes for JMP, CALL, and JBb

|      |     | First Byte                                  |     | Second Byte     |

|------|-----|---------------------------------------------|-----|-----------------|

| JMP  | Bit | 7 6 5 4 3 2 1 0<br>A <sub>H</sub> 0 0 1 0 0 | Bit | 7 6 5 4 3 2 1 0 |

| CALL | Bit | 7 6 5 4 3 2 1 0<br>A <sub>H</sub> 1 0 1 0 0 | Bit | 7 6 5 4 3 2 1 0 |

| JBb  | Bit | 7 6 5 4 3 2 1 0<br>B <sub>b</sub> 1 0 0 1 0 | Bit | 7 6 5 4 3 2 1 0 |

${f A_H}={f Address}\,{f A}_{10},\,{f A}_{9},\,{f A}_{8}$   ${f A}_{L}={f Address}\,{f A}_{7}$  to  ${f A}_{0}$   ${f Bb}={f b}^{th}$  bit of accumulator

#### **INSTRUCTION CODES**

| H L | 0              | 1              | 2            | 3             | 4             | 5            | 6             | 7             | 8                | 9                | A                | В                | С                | D                | Е                | F                |

|-----|----------------|----------------|--------------|---------------|---------------|--------------|---------------|---------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 0   | NOP            |                | OUT<br>DBB,A | ADD<br>A,#    | JMP<br>0 x x  | EN I         |               | DEC<br>A      |                  | IN<br>A, P1      | IN<br>A, P2      |                  | MOVD<br>A, P4    | MOVD<br>A, P5    | MOVD<br>A, P6    | MOVD<br>A, P7    |

| 1   | INC<br>@R0     | INC<br>@R1     | JB0<br>addr  | ADDG<br>A, #  | CALL<br>0 x x | DIS          | JTF<br>addr   | INC<br>A      | INC<br>R0        | INC<br>R1        | INC<br>R2        | INC<br>R3        | INC<br>R4        | INC<br>R5        | INC<br>R6        | INC<br>R7        |

| 2   | XCH<br>A, @R0  | XCH<br>A, @R1  | IN<br>A, DBB | MOV<br>A,#    | JMP<br>1 x x  | EN<br>TCNTI  | JNT0<br>addr  | CLR<br>A      | XCH<br>A, R0     | XCH<br>A, R1     | XCH<br>A, R2     | XCH<br>A, R3     | XCH<br>A, R4     | XCH<br>A, R5     | XCH<br>A, R6     | XCH<br>A, R7     |

| 3   | XCHD<br>A, @R0 | XCHD<br>A, @R1 | JB1<br>addr  |               | CALL<br>1 x x | DIS<br>TONTI | JT0<br>addr   | CPL<br>A      |                  | OUTL<br>P1, A    | OUTL<br>P2, A    |                  | MOVD<br>P4, A    | MOVD<br>P5, A    | MOVD<br>P6, A    | MOVD<br>P7. A    |

| 4   | ORL<br>A, @R0  | ORL<br>A, @R1  | MOV<br>A, T  | ORL<br>A,#    | JMP<br>2 x x  | STRT         | JNT1<br>addr  | SWAP<br>A     | ORL<br>A, R0     | ORL<br>A, R1     | ORL<br>A, R2     | ORL<br>A. R3     | ORL<br>A, R4     | ORL<br>A. R5     | ORL<br>A, R6     | ORL<br>A, R7     |

| 5   | ANL<br>A, @R0  | ANL<br>A, @R1  | JB2<br>addr  | ANL<br>A,#    | CALL<br>2 x x | STRT         | JT1<br>addr   | DA<br>A       | ANL<br>A, R0     | ANL<br>A, R1     | ANL<br>A, R2     | ANL<br>A, R3     | ANL<br>A, R4     | ANL<br>A, R5     | ANL<br>A, R6     | ANL<br>A, R7     |

| 6   | ADD<br>A, @R0  | ADD<br>A, @R1  | MOV<br>T, A  |               | JMP<br>3 x x  | STOP<br>TCNT |               | RRC<br>A      | ADD<br>A, R0     | ADD<br>A, R1     | ADD<br>A, R2     | ADD<br>A, R3     | ADD<br>A, R4     | ADD<br>A, R5     | ADD<br>A, R6     | ADD<br>A, R7     |

| 7   | ADDC<br>A, @R0 | ADDC<br>A, @R1 | JB3<br>addr  |               | CALL<br>3 x x |              | JF1<br>addr   | RR<br>A       | ADDC<br>A, R0    | ADDC<br>A, R1    | ADDC<br>A, R2    | ADDC<br>A. R3    | ADDC<br>A, R4    | ADDC<br>A, R5    | ADDC<br>A, R6    | ADDC<br>A, R7    |

| 8   |                |                |              | RET           | JMP<br>4 x x  | CLR<br>F0    | JOBF<br>addr  |               |                  | ORL<br>P1, #     | ORL<br>P2. #     |                  | ORLD<br>P4, A    | ORLD<br>P5. A    | ORLD<br>P6. A    | ORLD<br>P7. A    |

| 9   | MOV<br>STS, A  |                | JB4<br>addr  | RETR .        | CALL<br>4xx   | CPL<br>F0    | JNZ<br>addr   | CLR<br>C      |                  | ANL<br>P1, #     | ANL<br>P2,#      |                  | ANLD<br>P4, A    | ANLD<br>P5. A    | ANLD<br>P6, A    | ANLD<br>P7, A    |

| A   | MOV<br>@R0, A  | MOV<br>@R1, A  |              | MOVP<br>A. @A | JMP<br>5××    | CLR<br>F1    |               | CPL<br>C      | MOV<br>R0, A     | MOV<br>R1, A     | MOV<br>R2, A     | MOV<br>R3, A     | MOV<br>R4, A     | MOV<br>R5, A     | MOV<br>R6, A     | MOV<br>R7. A     |

| В   | MOV<br>@R0, #  | MOV<br>@R1,#   | JB5<br>addr  | JMPP<br>@A    | CALL<br>5 x x | CPL<br>F1    | JF0<br>addr   |               | MOV<br>R0, #     | MOV<br>R1, #     | MOV<br>R2. #     | MOV<br>R3, #     | MOV<br>R4, #     | MOV<br>R5. #     | MOV<br>R6, #     | MOV<br>R7, #     |

| С   |                |                |              |               | JMP<br>6××    | SEL<br>RB0   | JZ<br>addr    | MOV<br>A, PSW | DEC<br>R0        | DEC<br>R1        | DEC<br>R2        | DEC<br>R3        | DEC<br>R4        | DEC<br>R5        | DEC<br>R6        | DEC<br>R7        |

| D   | XRL<br>A, @R0  | XRL<br>A, @R1  | JB6<br>addr  | XAL<br>A,#    | CALL<br>6 x x | SEL<br>RB1   | JNIBF<br>addr | MOV<br>PSW, A | XRL<br>A, R0     | XRL<br>A, R1     | XRL<br>A, R2     | XRL<br>A, R3     | XRL<br>A, R4     | XRL<br>A, R5     | XRL<br>A, R6     | XRL<br>A, R7     |

| E   |                |                |              | MOVP3<br>A.@A | JMP<br>7 x x  | EN<br>DMA    | JNC<br>addr   | RL<br>A       | DJNZ<br>R0. addr | DJNZ<br>R1, addr | DJNZ<br>R2, addr | DJNZ<br>R3, addr | DJNZ<br>R4, addr | DJNZ<br>R5. addr | DJNZ<br>R6, addr | DJNZ<br>R7, addr |

| F   | MOV<br>A, @R0  | MOV<br>A, @R1  | JB7<br>addr  |               | CALL<br>7xx   | EN<br>FLAGS  | JC<br>addr    | RLC<br>A      | MOV<br>A, R0     | MOV<br>A, R1     | MOV<br>A, R2     | MOV<br>A. R3     | MOV<br>A. R4     | MOV<br>A. R5     | MOV<br>A, R6     | MOV<br>A. R7     |

# Legend: # = Immediate data = 1 Byte, 1 Cycle Instruction = 1 Byte, 2 Cycle Instruction

= 2 Byte, 2 Cycle Instruction

#### **ELECTRICAL CHARACTERISTICS**

#### **Absolute Maximum Ratings**

| Parameter                        | Symbol                               | Value        | Unit |  |

|----------------------------------|--------------------------------------|--------------|------|--|

| Supply Voltage                   | V <sub>CC</sub> ,<br>V <sub>DD</sub> | -0.3 to +7.0 | v    |  |

| Input Voltage                    | V <sub>IN</sub>                      | -0.3 to +7.0 | V    |  |

| Ambient Operating<br>Temperature | T <sub>A</sub>                       | 0 to +70     | ۰c   |  |

| Storage Temperature              | T <sub>stg</sub>                     | -55 to +150  | °C   |  |

| Power Dissipation                | P <sub>D</sub>                       | 1.5          | w    |  |

#### Note:

Permanent device damage may occur if the above ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the

#### **Recommended Operating Conditions**

|                          |                   |     | Value |     |      |

|--------------------------|-------------------|-----|-------|-----|------|

| Parameter                | Symbol            | Min | Тур   | Max | Unit |

| Supply Voltage           | V <sub>CC</sub> , | 4.5 | 5.0   | 5.5 | v    |

| ,                        | V <sub>SS</sub>   |     | 0     |     | v    |

| Operating<br>Temperature | T <sub>A</sub>    | 0   |       | +70 | °C   |

conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Characteristics**

$T_A$  = 0°C to +70°C,  $V_{CC}$  =  $V_{DD}$  = 5.0V  $\pm$  10%,  $V_{SS}$  = 0V

|                                | ·                                                                                                                   |                                   |                                                | Va   | lue             |      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------|------|-----------------|------|

| Pa                             | rameter                                                                                                             | Symbol                            | Test Conditions                                | Min  | Max             | Unit |

| V <sub>DD</sub> Supply Current |                                                                                                                     | I <sub>DD</sub>                   |                                                |      | 20              | mA   |

| Supply Current                 |                                                                                                                     | I <sub>CC</sub> + I <sub>DD</sub> |                                                |      | 150             | mA   |

| Innut I am Maltana             | All except XTAL1, 2, RESET                                                                                          | V <sub>IL</sub>                   |                                                | -0.3 | 0.8             | ٧    |

| Input Low Voltage              | XTAL1, 2, RESET                                                                                                     | V <sub>IL1</sub>                  |                                                | -0.3 | 0.6             | ٧    |

| Innut I link Makes             | All except XTAL1, 2, RESET                                                                                          | V <sub>IH</sub>                   |                                                | 2.0  | V <sub>CC</sub> | ٧    |

| Input High Voltage             | XTAL1, 2, RESET                                                                                                     | V <sub>IH1</sub>                  |                                                | 3.8  | V <sub>CC</sub> | V    |

|                                | D <sub>0</sub> to D <sub>7</sub>                                                                                    | V <sub>OL</sub>                   | I <sub>OL</sub> = 2.0mA                        |      | 0.45            | ٧    |

| Output Low Voltage             | P10 to P17, P20 to P27, SYNC                                                                                        | V <sub>OL1</sub>                  | I <sub>OL</sub> = 1.6mA                        |      | 0.45            | ٧    |

|                                | PROG                                                                                                                | V <sub>OL2</sub>                  | I <sub>OL</sub> = 1.0mA                        |      | 0.45            | ٧    |

| Output High Voltage            | D <sub>0</sub> to D <sub>7</sub>                                                                                    | V <sub>OH</sub>                   | I <sub>OH</sub> = -400μA                       | 2.4  |                 | ٧    |

| Output High Voltage            | All other outputs                                                                                                   | V <sub>OH1</sub>                  | I <sub>OH</sub> = -50μA                        | 2.4  |                 | ٧    |

| Input Leakage Current          | T <sub>0</sub> , T <sub>1</sub> , $\overline{\text{RD}}$ , $\overline{\text{WR}}$ , $\overline{\text{CS}}$ , A0, EA | I <sub>IL</sub>                   | $V_{SS} \le V_{IN} \le V_{CC}$                 |      | ±10             | μΑ   |

| Output Leakage Current         | D <sub>0</sub> to D <sub>7</sub> (High-impedance)                                                                   | loL                               | $V_{SS}$ + 0.45V $\leq$ $V_{IN} \leq V_{CC}$ . |      | ±10             | μΑ   |

| Innut I am Comment             | P10 to P17; P20 to P27                                                                                              | ILI                               | V <sub>IL</sub> = 0.8V                         |      | 0.5             | mA   |

| Input Low Current              | RESET, SS                                                                                                           | I <sub>LI1</sub>                  | V <sub>IL</sub> = 0.8V                         |      | 0.2             | mA   |

# MBL8742H/N

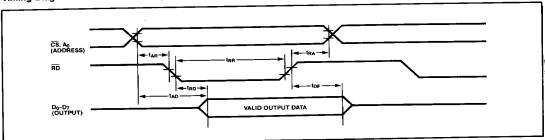

# AC Characteristics (DBB Read Operation)

$(T_A = 0^{\circ}\text{C to} + 70^{\circ}\text{C}, V_{CC} = V_{DD} = 5.0\text{V} \pm 10\%, V_{SS} = 0\text{V})$

|                               |          |                 |                        | Value |      |      |

|-------------------------------|----------|-----------------|------------------------|-------|------|------|

| Parameter                     |          | Symbol          | ol Test Conditions     | Min   | Max  | Unit |

| CS, A0 Setup Time (to RD ↓)   |          | t <sub>AR</sub> |                        | 0     |      | ns   |

| CS. A0 Hold Time (to RD↑)     |          | t <sub>RA</sub> |                        | 0     |      | ns   |

| RD Pulse Width                |          | t <sub>RR</sub> |                        | 160   |      | ns   |

| Data Delay Time (from CS, A0) |          | t <sub>AD</sub> | C <sub>L</sub> = 150pF |       | 130  | ns   |

| Data Delay Time (from RD ↓)   |          | t <sub>RD</sub> | C <sub>L</sub> = 150pF |       | 130  | ns   |

| Data Floating Time (from RD↑) |          | t <sub>DF</sub> |                        |       | 85   | ns   |

|                               | MBL8742N |                 | 6MHz (N-version)       | 2.5   | 15.0 | μs   |

| Cycle Time                    | MBL8742H | t <sub>CY</sub> | 12MHz (H-version)      | 1.25  | 15.0 | μs   |

# Timing Diagram for Data Bus Buffer (DBB) Read Operation:

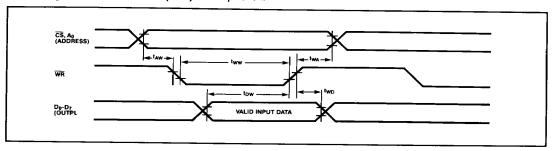

# AC Characteristics (DBB Write Operation) ( $T_A = 0$ °C to +70°C, $V_{CC} = V_{DD} = 5.0V \pm 10$ %, $V_{SS} = 0$ V)

| Parameter                   | ·               |                 | Value |     |      |

|-----------------------------|-----------------|-----------------|-------|-----|------|

|                             | Symbol          | Test Conditions | Min   | Max | Unit |

| CS, A0 Setup Time (to WR ↓) | t <sub>AW</sub> |                 | 0     |     | ns   |

| CS, A0 Hold Time (from WR↑) | t <sub>WA</sub> |                 | 0     | -   | ns   |

| WR Pulse Width              | t <sub>ww</sub> |                 | 160   | _   | ns   |

| Data Setup Time (to WR↑)    | t <sub>DW</sub> |                 | 130   |     | ns   |

| Data Hold Time (from ₩R ↑)  | t <sub>WD</sub> |                 | 0     |     | ns   |

#### Timing Diagram for Data Bus Buffer (DBB) Write Operation:

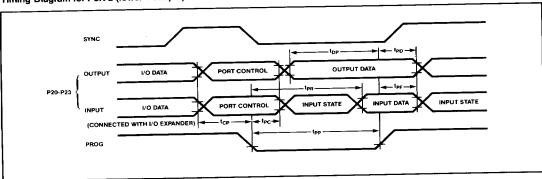

# AC Characteristics (Operation with I/O Expander)

(T<sub>A</sub> = 0°C to +70°C,  $V_{CC}$  =  $V_{DD}$  = 5.0V ±10%, $V_{SS}$  = 0V)

| Parameter                            |                 | MBL | 8742N | MBL8742H |     |      |

|--------------------------------------|-----------------|-----|-------|----------|-----|------|

|                                      | Symbol          | Min | Max   | Min      | Max | Unit |

| Port Control Setup Time (to PROG ↓)  | t <sub>CP</sub> | 100 |       | 110      |     | ns   |

| Port Control Hold Time (from PROG ↓) | t <sub>PC</sub> | 60  |       | 100      |     | ns   |

| Input Data Delay Time (from PROG ↓)  | t <sub>PR</sub> |     | 650   |          | 810 | ns   |

| Input Data Hold Time (from PROG ↑)   | tpf             | 0   | 150   | 0        | 150 | ns   |

| Output Data Setup Time (to PROG ↑)   | t <sub>DP</sub> | 200 |       | 250      |     | ns   |

| Output Data Hold Time (from PROG ↑)  | t <sub>PD</sub> | 20  |       | 65       |     | ns   |

| PROG Pulse Width                     | t <sub>PP</sub> | 700 |       | 1200     |     | ns   |

# Timing Diagram for Port 2 (lower 4 bits) Operation in Connection With I/O Expander:

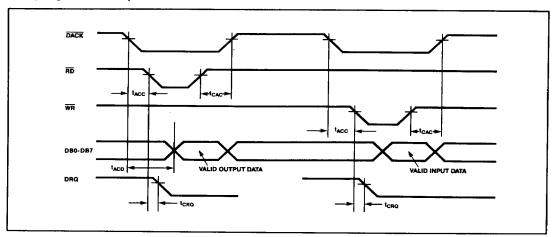

### **AC Characteristics (DMA Operation)**

$(T_A = 0^{\circ}C \text{ to } + 70^{\circ}C, V_{CC} = V_{DD} = 5.0V \pm 10\%, V_{SS} = 0V)$

| Parameter                           |                  |                        | Va      | lue  |    |

|-------------------------------------|------------------|------------------------|---------|------|----|

|                                     | Symbol           | Test Conditions        | Min Max | Unit |    |

| DACK Setup Time (to RD ↓, WR ↓)     | t <sub>ACC</sub> |                        | 0       |      | ns |

| DACK Hold Time (from RD ↑, WR ↑)    | t <sub>CAC</sub> |                        | 0       |      | ns |

| Input Data Delay Time (from DACK ↓) | t <sub>ACD</sub> | C <sub>L</sub> = 150pF |         | 130  | ns |

| DRQ Clear Time (from RD ↓, WR ↓)    | †CRQ             |                        | <b></b> | 100  | ns |

#### Timing Diagram for DMA Operation:

#### **TEST CONDITIONS**

V<sub>IL</sub> = 0.8V (All except XTAL1, 2, RESET) = 0.6V (XTAL1, 2, RESET)

V<sub>IH</sub> = 2.0V (All except XTAL1, 2, RESET)

= 3.8V (XTAL1, 2, RESET)

V<sub>OL</sub> = 0.45V

V<sub>OH</sub> = 2.4V

OUTPUT LOAD

D0 to D7:  $C_L = 150pF$ All other outputs:  $C_L = 80pF$

#### **Oscillation Circuits**

4-180

# **ELECTRICAL CHARACTERISTICS FOR PROGRAMMING**

#### DC Characteristics1,2

(T<sub>A</sub> = 25°C  $\pm$ 5°C, V<sub>CC</sub> = 5V  $\pm$ 5%, V<sub>DD</sub> = 21  $\pm$ 0.5V or 5V  $\pm$ 5%)

| A 20 0 0 0 0                                |                   | Va   | lue  |          |

|---------------------------------------------|-------------------|------|------|----------|

| Parameter                                   | Symbol            | Min  | Max  | Unit     |

| V <sub>DD</sub> Program Voltage High Level  | V <sub>DDH</sub>  | 20.5 | 21.5 | Ŭ v      |

| V <sub>DD</sub> Program Voltage Low Level   | V <sub>DDL</sub>  | 4.75 | 5.25 |          |

| PROG Program Voltage High Level             | V <sub>PH</sub>   | 17.5 | 18.5 | _ v      |

| PROG Program Voltage Low Level              | V <sub>PL</sub>   | _    | 0.2  | <u> </u> |

| EA Program/Verify Voltage High Level        | V <sub>EAH</sub>  | 17.5 | 18.5 | _ v      |

| EA Program/Verify Voltage Low Level         | V <sub>EAL</sub>  |      | 5.25 |          |

| V <sub>DD</sub> High Voltage Supply Current | I <sub>DD</sub>   |      | 30.0 |          |

| PROG High Voltage Supply Current            | I <sub>PROG</sub> | _    | 16.0 | mA       |

| EA High Voltage Supply Current              | I <sub>EA</sub>   | _    | 1.0  |          |

1. High Level Voltage ( $V_{DDH}$ ,  $V_{PH}$ ) should not be applied to  $V_{DD}$  and PROG pins unless  $V_{CC}=5V\pm5\%$  and EA = 18V  $\pm0.5V$ . 2.  $V_{DD}$ , PROG, and EA should not exceed the above specified range, including overshoot and undershoot.

#### **AC Characteristics**

$(T_A = 25^{\circ}C \pm 5^{\circ}C, V_{CC} = 5V \pm 5\%, V_{DD} = 21 \pm 1.0V \text{ or } 5V \pm 5\%)$

| <del></del>                                |                   | Val                 | ue                  | _    |

|--------------------------------------------|-------------------|---------------------|---------------------|------|

| Parameter                                  | Symbol            | Min                 | Max                 | Unit |

| Address setup time (before RESET↑)         | t <sub>AW</sub>   | 4 · t <sub>CY</sub> |                     |      |

| Address hold time (after RESET ↑)          | t <sub>WA</sub>   | 4 · t <sub>CY</sub> |                     |      |

| Input data setup time (before PROG ↑)      | t <sub>DW</sub>   | 4 · t <sub>CY</sub> |                     | -    |

| input data hold time (after PROG 1)        | t <sub>WD</sub>   | 4 · t <sub>CY</sub> |                     |      |

| RESET hold time (after EA ↓)               | t <sub>PH</sub>   | 4 · t <sub>CY</sub> | _                   |      |

| V <sub>DD</sub> setup time (before PROG ↑) | t <sub>VDDW</sub> | 4 · t <sub>CY</sub> |                     |      |

| V <sub>DD</sub> hold time (before PROG ↓)  | t <sub>VDDH</sub> | 0                   | _                   |      |

| Program pulse width                        | t <sub>PW</sub>   | 50                  | 60                  | ms   |

| TO setup time (before RESET ↑)             | t <sub>TW</sub>   | 4 · t <sub>CY</sub> |                     |      |

| TO hold time (after V <sub>DD</sub> ↓)     | ŧwт               | 4 · t <sub>CY</sub> |                     |      |

| Data output delay time (after TO ↑)        | t <sub>DO</sub>   |                     | 4 · t <sub>CY</sub> | ļ    |

| RESET pulse width (to Latch Address)       | tww               | 4 · t <sub>CY</sub> |                     |      |

| V <sub>DO</sub> and PROG rise/fall time    | tr/tf             | 0.5                 | 2.0                 | μs   |

| MPU cycle time                             | t <sub>CY</sub>   | 5.0                 | _                   | μs   |

| RESET setup time (before EA ↑)             | t <sub>RE</sub>   | 4 · t <sub>CY</sub> |                     | _    |

| EA setup time (before RESET 1)             | t <sub>EA</sub>   | 10                  |                     | ms   |

#### Timing Diagram for Programming/Verify Mode:

#### PACKAGE DIMENSIONS

4-182